并行接口芯片8255A内部结构和引脚功能概述IC解密

8255A芯片 Intel 8086/8088 系列的可编程外设接口电路(Programmable Peripheral Interface)简称 PPI,型号为8255(改进型为8255A及8255A-5),具有24条输入/输出引脚、可编程的通用并行输入/输出接口电路。它是一片使用单一+5V电源的40脚双列直插式大规模集成电路。

8255A是一种可编程的并行I/O接口。IC解密与简单I/O接口不同,可编程的I/O接口通常有多种工作模式,单片机可以通过程序设置其具体的工作模式或状态。

8255A的内部结构和引脚

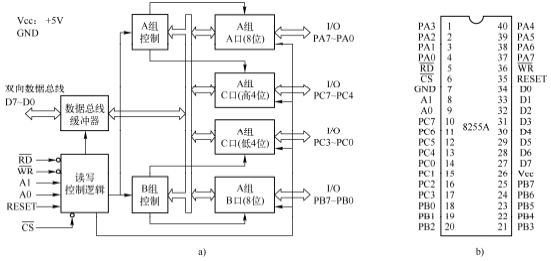

8255A的功能结构和引脚如图5-18所示。

图5-18 8255A的功能结构图和引脚图

a)功能结构图b)引脚图

1.8255A的功能结构

(1)并行I/O口

8255A有3个8位并行的I/O口,IC解密即A口、B口和C口,这些I/O口又被分为A组和B组,分别由A组控制器和B组控制器控制,其中:A组由A口的8位和C口的高4位构成;B组由B口的8位和C口的低4位构成。

(2)数据总线缓冲器

8255A的数据总线缓冲器是双向、三态的缓冲器。通过该缓冲器,8255A既可以接收来自于单片机的控制命令字,也可以将自身的信息传送给单片机。更重要的是,利用该缓冲器,单片机可以与8255A的A口、B口和C口之间进行数据交换,从而扩展单片机自身的并行I/O口。

(3)读写控制逻辑

单片机可以通过读写控制逻辑对8255A进行操作,如:对8255A进行复位操作或向8255A的A口发送数据等。

2.8255A的引脚功能

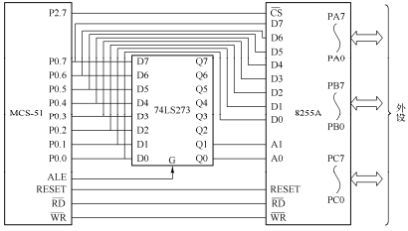

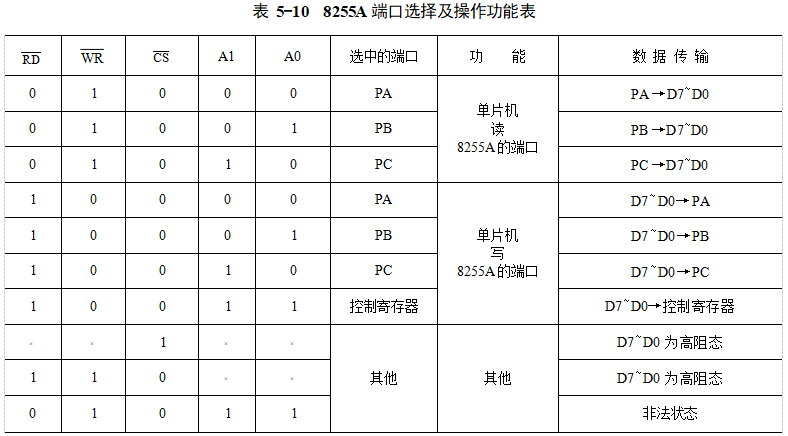

本小节将结合单片机与8255A的连接图(见图5-19),IC解密以及表5-10所示的8255A端口选择和操作功能,讲解8255A的引脚功能。

图5-19 8255A与单片机的引脚连接

(1)并行I/O端口

PA、PB和PC分别是8255A的A口、B口和C口所对应的8位并行输入/输出引脚。通常PA、PB和PC与单片机的外设相连,负责与单片机的外设交换数据。

(2)数据总线D7~D0

D7~D0是8255A的8位双向数据总线引脚,与单片机的数据总线相连。单片机通过该引脚向8255A发送控制命令。另外,单片机可以通过D7~D0与8255A的A、B或C口交换数据。

(3)读写信号RD和WR

低电平有效的RD和WR引脚分别是8255A的读信号和写信号引脚,并分别与MCS-51单片机的RD和WR引脚相连。当RD为低电平时,单片机从8255A读取数据,8255A D7~D0引脚上的数据传输方向为由8255A至单片机。反之,当WR为低电平时,数据传输方向为由单片机到8255A。

与访问简单I/O接口相同,MCS-51单片机通过MOVX指令访问可编程的8255A。执行“MOVX A,@DPTR”或“MOVX A,@Ri”指令时,MCS-51单片机读取8255A并行端口上的数据,此时单片机的RD引脚为低电平。执行“MOVX@DPTR,A”或“MOVX@Ri,A”指令时,MCS-51单片机写数据到8255A,此时单片机的WR引脚为低电平。

(4)地址线A0和A1

8255A有4个I/O端口,包括:A口、B口、C口和接收单片机控制命令的控制字寄存器。当单片机访问8255A时,8255A引脚A0和A1的状态决定了单片机访问的具体是哪一个端口,见表5-10。

(5)片选信号CS

片选信号CS低电平有效,该引脚为低电平时8255A才能够工作。通常,该引脚与单片机的地址线相连,用于单片机对8255A的选择控制。在图5-19所示电路中,当单片机的P2.7引脚输出低电平时,8255A被单片机选中并工作。

(6)复位引脚RESET

复位引脚RESET高电平有效。8255A复位时,其控制寄存器将被清0,其所有的并行I/O端口PA、PB和PC均被设置为输入。

如图5-19所示,当单片机读取外设数据时,外设数据首先进入8255A的某个指定数据端口(由地址选定的A口、B口或C口),然后通过8255A的数据总线(D7~D0)进入单片机;而单片机向外设发送数据时,单片机的数据首先通过数据总线(D7~D0)到达8255A某个指定数据端口,然后通过这个端口送给外设。由此可知,8255A仅是单片机与外设之间数据传输的通道,IC解密并不会对数据本身产生任何影响。

本公司声明: 本文章由作者或相关机构授权发布,目的在于传递更多信息,并不代表本公司赞同其观点,本公司亦不保证或承诺内容真实性等。需要转载请联系该专栏作者,如若文章内容侵犯您的权益,请及时联系本公司删除。

芯片解密

芯片解密